// Data Memory

module dmem(clk, wr, addr, din, dout);

input clk, wr;

input [3:0] addr, din;

output [3:0] dout;

reg [3:0] mem[0:15];

always @(posedge clk) begin

// operation

// ....

end

assign dout = .....;

endmodule

偙偙偱億僀儞僩偼丄5峴栚偺儊儌儕偺幚懱偱偁傞曄悢mem偺愰尵偱偡丅

乽reg [3:0]乿偲偡傞偙偲偱丄4價僢僩暆偺曄悢(reg宆)偑愰尵偱偒傑偡偑丄

偙傟傪乽mem[0:15]乿偲偡傞偙偲偱丄15屄暘偺攝楍偲偟偰愰尵偟偰偄傑偡丅

偡側傢偪mem偼4價僢僩亊15屄偺攝楍丄偲偄偆偙偲偵側傝傑偡丅

偪側傒偵mem[0]偼0斣抧偺僨乕僞4價僢僩丄mem[0][3]偼

偦偺0斣抧偺僨乕僞偺嵟忋埵價僢僩丄偲側傝傑偡丅

偙傟偼師偺傛偆側擇師尦攝楍偲峫偊傞偲傢偐傝傗偡偄偱偟傚偆丅

| 0斣抧 | mem[0][3] | mem[0][2] | mem[0][1] | mem[0][0] | 仼4價僢僩傑偲傔偰mem[0] |

| 1斣抧 | mem[1][3] | mem[1][2] | mem[1][1] | mem[1][0] | 仼4價僢僩傑偲傔偰mem[1] |

| ... | ... | ... | ... | ... | ... |

| 15斣抧 | mem[15][3] | mem[15][2] | mem[15][1] | mem[15][0] | 仼4價僢僩傑偲傔偰mem[15] |

| 柦椷(op) | 僯乕儌僯僢僋昞婰 | 摦嶌撪梕 |

| 0000 | mov imm, r0 | imm傪r0偵戙擖 |

| 0001 | mov imm, r1 | imm傪r1偵戙擖 |

| 0010 | add r0, imm, r0 | r0+imm傪r0偵戙擖 |

| 0011 | add r0, imm, r1 | r0+imm傪r1偵戙擖 |

| 0100 | add r1, imm, r0 | r1+imm傪r0偵戙擖 |

| 0101 | add r1, imm, r1 | r1+imm傪r1偵戙擖 |

| 0110 | jmp imm | imm斣抧傊僕儍儞僾(柍忦審暘婒) |

| 0111 | jz imm | Z僼儔僌=1側傜偽imm斣抧傊暘婒丄偦傟埲奜偼師偺柦椷傊 |

| 1000 | mov r0, @imm | r0偺撪梕傪僨乕僞儊儌儕偺imm斣抧傊彂偒崬傒 |

| 1001 | mov r1, @imm | r1偺撪梕傪僨乕僞儊儌儕偺imm斣抧傊彂偒崬傒 |

| 1010 | mov @imm, r0 | 僨乕僞儊儌儕偺imm斣抧偺撪梕傪r0傊戙擖 |

| 1011 | mov @imm, r1 | 僨乕僞儊儌儕偺imm斣抧偺撪梕傪r1傊戙擖 |

module sample(CLK6, LED, SW, SG, SA);

input CLK6;

input [3:0] SW;

output [7:0] LED, SG;

output [3:0] SA;

reg [3:0] r0, r1, pc, daddr, d2io;

wire [3:0] iaddr, d2cpu, op, imm;

wire [7:0] idata;

wire [3:0] d3, d2, d1, d0;

reg mem_wr, st, z;

wire clk, rst;

imem i0(iaddr, idata);

dmem i1(clk, mem_wr, daddr, d2io, d2cpu);

sw_clk iclk(CLK6, ~SW[0], clk);

seg7 iseg7(CLK6, d3, d2, d1, d0, SG, SA);

assign LED = {z, st, clk, 1'b0, op};

assign d0 = r0, d1 = r1, d2 = iaddr, d3 = daddr;

assign rst = ~SW[3];

assign iaddr = pc;

assign op = idata[7:4], imm = idata[3:0];

always @(posedge clk or posedge rst) begin

if (rst == 1'b1) begin

pc <= 4'h0; st <= 1'b0; z <= 1'b0; mem_wr <= 1'b0; daddr <= 4'h0; r0 <= 4'h0; r1 <= 4'h0;

end

else begin

if (st == 0) begin

st <= 1'b1;

mem_wr <= 1'b0;

case (op)

// operation

// resister access, mem_wr setf for op=1000/1001

....

endcase

end

else begin

st <= 1'b0;

// memory read for op=1010/1011

case (op)

...

endcase

// update pc

if (op == 4'b0110) ...

end

end

end

endmodule

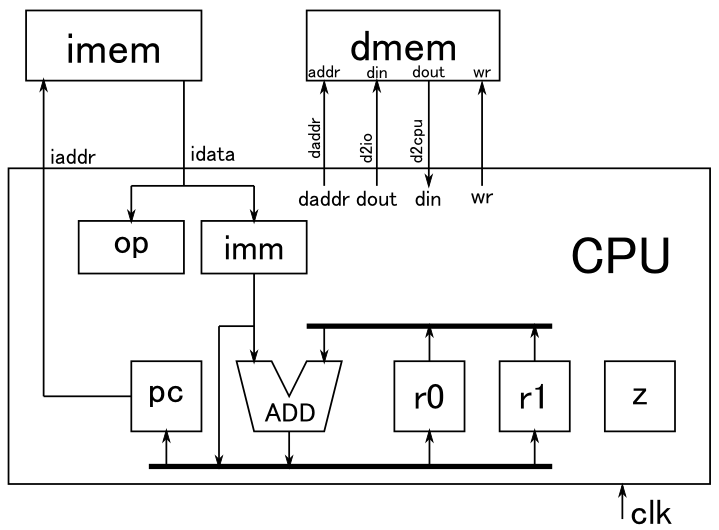

墘廗3-2 sample_cpu2.zip傪僟僂儞儘乕僪偟偰揥奐偟丄 偙偺拞偺sample.v傪嶲峫偵丄偙傟傜偺柦椷傪奼挘偟偨CPU傪 愝寁偟偰傒傑偟傚偆丅 僨乕僞儊儌儕dmem偼丄慜夞偲摨條偵怴偟偄VerilogHDL僼傽僀儖mem.v傪 僾儘僕僃僋僩偵捛壛偟丄偙偺拞偵柦椷儊儌儕imem偺婰弎偲偲傕偵 婰弎偡傞偲傛偄偱偟傚偆丅 傑偨偙傟偵埲壓偺傛偆側僾儘僌儔儉(傕偭偲挿偄僾儘僌儔儉偱傕傛偄)傪 柦椷儊儌儕imem撪偵婰弎偟偰丄偙傟傪幚峴偝偣偰傒傑偟傚偆丅 (偙偺僾儘僌儔儉偱偼丄嵟廔揑偵r1=1偲側傞偙偲偵側傞)

| 斣抧(iaddr) | 柦椷(idata) | 柦椷偺僯乕儌僯僢僋昞婰 |

| 0 | 0000 0001 | mov 1, r0 |

| 1 | 1000 0011 | mov r0, @3 |

| 2 | 1011 0011 | mov @3, r1 |

| 3 | 0110 0011 | jmp 3 |

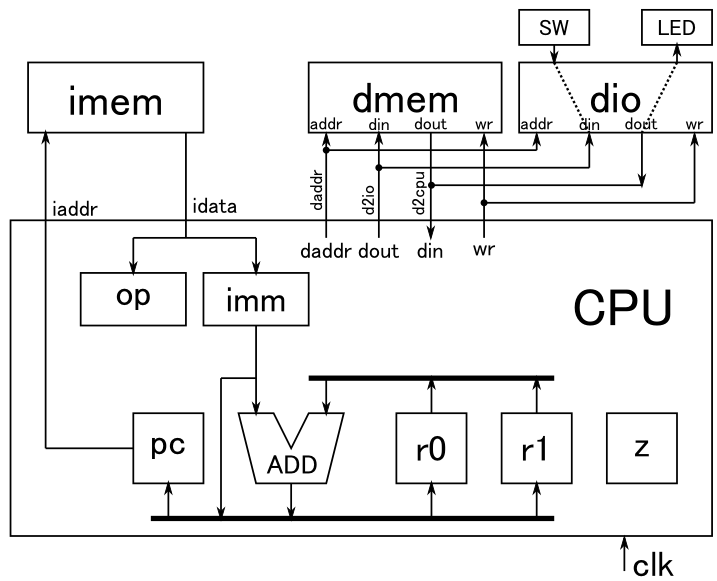

僨乕僞儊儌儕偺堦晹傪丄LED側偳偺I/O僨僶僀僗偺傛偆偵埖偆偙偲傪 乽儊儌儕儅僢僾僪(Memory-mapped I/O)乿偲屇傃傑偡丅 偙偙偱偼丄僨乕僞儊儌儕偺摿掕偺斣抧偵僨乕僞傪彂偒崬傓偲丄 偦偺抣偑捈愙LED偵昞帵偝傟傞傛偆側夞楬dio傪愝寁偟偰傒傑偟傚偆丅

偲偄偭偰傕儊儌儕儅僢僾僪I/O偺弌椡懁(CPU偐傜彂偒崬傑傟傞懁)偼丄 婎杮揑偵偼僨乕僞儊儌儕偺彂偒崬傒晹暘偲慡偔摨偠偱偡丅 椺偊偽師偺傛偆側夞楬傪dio.v偲偟偰僾儘僕僃僋僩偵捛壛偟偰偍偒傑偡丅

module dio(clk, wr, addr, din, d_led);

input clk, wr;

input [3:0] addr, din;

output [3:0] d_led;

reg [3:0] d_led;

always @(posedge clk) begin

if (wr == 1'b1) if (addr == 4'hf) d_led <= din;

end

endmodule

拞傪撉傓偲傢偐傞偲偍傝丄addr=4'hf (2恑悢偱1111丄10恑悢偱15)斣抧傊偺

乽彂偒崬傒乿偵懳偟偰偼丄偦偺彂偒崬傫偩僨乕僞傪

弌椡d_led偵弌椡偡傞(偦偟偰偦偺抣傪曐帩偡傞)丄偲偄偆摦嶌傪偡傞傛偆側

婰弎偵側偭偰偄傑偡丅

CPU杮懱偺傎偆偱偼丄師偺傛偆偵偙偺夞楬dio傪屇傃弌偟偰偍偒丄

傾僪儗僗丄僨乕僞偵偼dmem偲摨條偵丄傾僪儗僗daddr偲

CPU偐傜dmem傊岦偐偆僨乕僞偲摨偠d2io傪偮側偄偱偍偒傑偡丅

弌椡d_led偼丄wire偲偟偰愰尵傪偟偰偍偒傑偟傚偆丅

wire [3:0] d_led;

dio i2(clk, mem_wr, daddr, d2io, d_led);

偙偺弌椡d_led偼丄7僙僌儊儞僩LED傗LED偺偁偄偰偄傞偲偙傠偵

assign偱偮側偄偱偍偄偰昞帵偝偣傞偙偲偵偟傑偡丅

墘廗3-3 儊儌儕儅僢僾僪I/O偺夞楬傪愝寁偟丄CPU偲偁傢偣偰摦嶌偝偣偰傒傑偟傚偆丅 偦偺摦嶌傪妋擣偱偒傞揔摉側僾儘僌儔儉傪imem偵奿擺偝偣傞偙偲丅 傑偨儊儌儕儅僢僾僪I/O傪奼挘偟丄妱傝摉偰斣抧傪曄峏偟偨傝 暋悢偺彂偒崬傒僨僶僀僗傗撉傒弌偟僨僶僀僗傪愝寁偟偰摦嶌偝偣偰傒傑偟傚偆丅

仸僸儞僩丗撉傒弌偟僨僶僀僗偼丄僨乕僞儊儌儕偺摿掕偺傾僪儗僗偵

懳偡傞撉傒弌偟偺嵺偵丄擖椡怣崋(椺偊偽僗僀僢僠偺抣)傪

撉傒弌偟僨乕僞d2cpu偵曉偡傛偆偵偡傟偽傛偄丅

偨偩偟僨乕僞儊儌儕dmem偐傜CPU傊岦偐偆僨乕僞d2cpu偲丄

偙偺dio偐傜CPU傊岦偐偆僨乕僞d2cpu偼摨堦偺怣崋慄偱偁傞偨傔丄

dmem偲dio偺椉曽偑d2io偵僨乕僞傪乽弌椡乿偟傛偆偲偡傞偲丄

乽嫞崌乿(CPU傊偺撉傒弌偟僨乕僞怣崋d2cpu偵丄僨乕僞儊儌儕dmem偲偙偺撉傒弌偟僨僶僀僗偺

2偮偑摨帪偵抣傪弌偦偆偲偡傞偲丄僀儞僾儕儊儞僥乕僔儑儞帪偵僄儔乕偑婲偙傞偐丄

摦嶌偝偣傜傟偰傕嵟埆偺応崌屘忈偡傞)偡傞偙偲偵側傞丅

偦偺偨傔丄僨乕僞儊儌儕偺d2cpu傊偺抣偺弌椡偼

傾僪儗僗daddr偑僨乕僞儊儌儕懳徾偺抣偺偲偒偩偗丄偲偟丄

偦傟埲奜偺偲偒偼師偺傛偆偵乽愙懕偟偰偄側偄(崅僀儞僺乕僟儞僗Z)乿偲偄偆抣傪

弌椡偡傞傛偆偵偡傞丅

assign dout = (addr == 5)?(4'bZZZZ):(mem[addr]);偙偺椺偱偼丄C尵岅偱偺乽?:乿墘嶼巕偲摨條偵丄 addr=5偺応崌偼4價僢僩偺Z(崅僀儞僺乕僟儞僗)傪丄 偦傟埲奜偺応崌偼僨乕僞儊儌儕偺撪梕傪d2cpu傊弌椡偡傞傛偆偵偟偰偄傞丅 崅僀儞僺乕僟儞僗偺堄枴偼丄師偺恾偺傛偆偵峫偊傞偲傛偄丅

assign dout = (addr == 5)?(....):(4'bZZZZ);