CPU偺傾乕僉僥僋僠儍偲婎杮愝寁

僐儞僺儏乕僞偺怱憻晹偲傕尵偊傞CPU (Centrol Processing Unit丄

MPU (Micro Processing Unit)偲傕屇傇)偼丄

儊儌儕撪偺僾儘僌儔儉傪弴偵幚峴偡傞傢偗偱偡偑丄

偙傟偼丄榑棟夞楬偲偟偰偼僗僥乕僩儅僔儞(忬懺慗堏夞楬)偲

傒側偡偙偲偑偱偒傑偡丅

偡側傢偪丄柦椷偵墳偠偰師偺摦嶌偑曄傢傞丄偝傜偵偦偺柦椷傪

幚峴偡傞僗僥僢僾偱偁傞儊儌儕偐傜偺撉傒崬傒(Fetch)傗

柦椷偺夝庍(Decode)側偳傕丄忬懺偺慗堏偲峫偊傞偙偲偑偱偒傑偡丅

偙偙偱偼丄奆偝傫偑忣曬僔僗僥儉岺妛幚尡戞2偺乽2-4.CPU偺峔惉乿偱

巊偭偨CPU偲帡偨傾乕僉僥僋僠儍偺CPU傪愝寁偟丄

幚嵺偵FPGA忋偱摦嶌偝偣偰傒傑偟傚偆丅

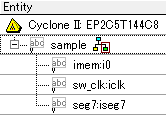

愝寁偡傞CPU偺傾乕僉僥僋僠儍

傾乕僉僥僋僠儍奣梫

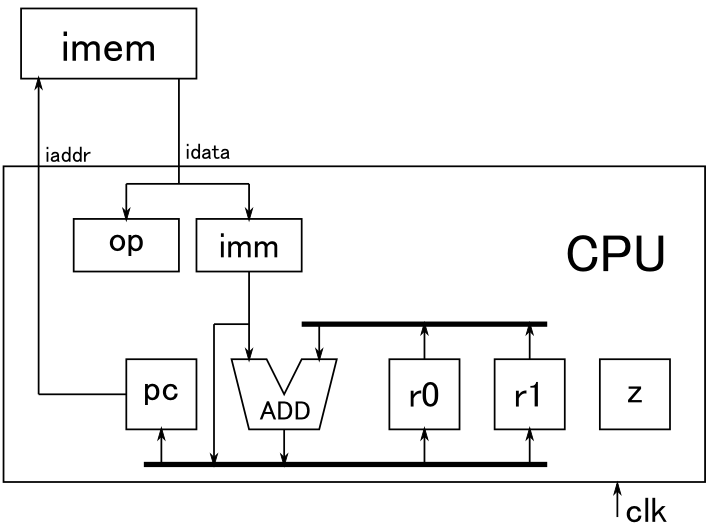

崱夞愝寁偡傞CPU偼丄忋恾偺傛偆側傾乕僉僥僋僠儍偲偟傑偡丅

庡側巇條偼埲壓偺捠傝偱偡丅

- 僨乕僞僶僗丄傾僪儗僗僶僗偼4價僢僩

- 撪憼儗僕僗僞偼r0, r1偺2偮(奺4價僢僩)

- 墘嶼偼壛嶼偺傒

- 忦審暘婒柦椷偁傝(Z僼儔僌)

- 柦椷傾乕僉僥僋僠儍偼丄柦椷(僆儁僐乕僪)4價僢僩偲懄抣(僆儁儔儞僪)4價僢僩偺8價僢僩屌掕挿丅

柦椷僙僢僩偺掕媊

幚峴偱偒傞柦椷偼丄4價僢僩偺僆儁僐乕僪(op)偵懳偟偰丄柦椷拞偺懄抣(imm)傪梡偄偰師偺傛偆偵掕媊偟傑偡丅(幚峴柦椷偺昞婰偱偁傞僯乕儌僯僢僋昞婰偲偁傢偣偰帵偡)

| 柦椷(op) | 僯乕儌僯僢僋昞婰 | 摦嶌撪梕 |

| 0000 | mov imm, r0 | imm傪r0偵戙擖 |

| 0001 | mov imm, r1 | imm傪r1偵戙擖 |

| 0010 | add r0, imm, r0 | r0+imm傪r0偵戙擖 |

| 0011 | add r0, imm, r1 | r0+imm傪r1偵戙擖 |

| 0100 | add r1, imm, r0 | r1+imm傪r0偵戙擖 |

| 0101 | add r1, imm, r1 | r1+imm傪r1偵戙擖 |

| 0110 | jmp imm | imm斣抧傊僕儍儞僾(柍忦審暘婒) |

| 0111 | jz imm | Z僼儔僌=1側傜偽imm斣抧傊暘婒丄偦傟埲奜偼師偺柦椷傊 |

椺偊偽丄儊儌儕偐傜撉傒弌偟偨柦椷idata偲柦椷偺僯乕儌僯僢僋昞婰丄幚峴撪梕偲偺懳墳偼埲壓偺捠傝偲側傝傑偡丅

- "0000 0001" : mov 1, r0 (儗僕僗僞r0偵抣1傪戙擖) (op="0000"丄imm="0001")

- "0010 0100" : add r0, 4, r0 (r0+4傪r0偵戙擖)

- "0110 0011" : jmp 3 (3斣抧傊僕儍儞僾)

- "0111 0100" : jz 4 (Z=1側傜偽4斣抧傊暘婒丄Z=0側傜偽師偺柦椷傊)

偙傟傜偺柦椷偼柦椷儊儌儕(Instruction Memory; imem)偵奿擺偝傟偰偄傞偲偟傑偡丅

(偙偺imem撪偺柦椷偺暲傃偑僾儘僌儔儉丄偲偄偆偙偲偵側傝傑偡)

尰嵼幚峴偟偰偄傞柦椷偑擖偭偰偄傞傾僪儗僗(iaddr)偼丄

僾儘僌儔儉僇僂儞僞(pc)偺抣丄偲偟傑偡丅

柦椷儊儌儕偼丄傾僪儗僗iaddr傪巜掕偡傞偲偦偺斣抧偵擖偭偰偄傞

柦椷傪idata偲偟偰曉偡夞楬丄偲傒傞偙偲偑偱偒傑偡偺偱丄

CPU偑峴偆傋偒摦嶌偲偟偰偼丄idata偺抣偵墳偠偰

儗僕僗僞偵彂偒崬傫偩傝暘婒偟偨傝丄偲偄偭偨摦嶌傪峴偆丄偙偲偵側傝傑偡丅

傑偨儗僕僗僞r0, r1傗pc偺抣側偳傪奜晹偐傜娤應偱偒傞傛偆偵偟偨傎偆偑

摦嶌妋擣偵偼曋棙偱偡偺偱丄7僙僌儊儞僩LED(4寘)傗8屄偺LED偵

昁梫側傕偺傪昞帵偝偣傞偙偲偵偟傑偡丅

側偍慡懱偺摦嶌偼僋儘僢僋怣崋clk偵偁傢偣偰峴偆偲偟丄

偙偺clk偼僗僀僢僠SW[0]偱嶌惉偡傞偙偲偵偟傑偡丅

偙偺僋儘僢僋偲7僙僌儊儞僩LED昞帵偼丄儔僀僽儔儕偲偟偰

peripheral.v傪梡堄偟偰偍偒傑偡偺偱丄偙傟傪巊偄傑偡丅

柦椷偺幚峴僒僀僋儖

1偮偺柦椷傪幚峴偡傞偺偵丄師偺2僗僥僢僾偱幚峴偡傞丄偲掕媊偟傑偡丅

(偆傑偔傗傞偲1僗僥僢僾偱幚峴偱偒傞偺偱偡偑丄

崱屻偺奼挘偺偨傔偵2僗僥僢僾幚峴偲偟偰偍偒傑偡)

側偍st偼丄奺僗僥僢僾偺忬懺傪嬫暿偡傞曄悢偲偟傑偡丅

- 僗僥僢僾0(st=0) : 柦椷偺撉傒庢傝丄儗僕僗僞傊偺戙擖丄Z僼儔僌偺愝掕

- 僗僥僢僾1(st=1) : 僾儘僌儔儉僇僂儞僞(pc)偺峏怴

CPU偺HDL愝寁

CPU偺HDL婰弎偺僥儞僾儗乕僩

僾儘僕僃僋僩偺僥儞僾儗乕僩sample_cpu.zip傪僟僂儞儘乕僪偟偰揥奐偟偰偍偒傑偡丅

偙偺僩僢僾奒憌偺sample.v偼師偺傛偆偵側偭偰偄傑偡丅

module sample(CLK6, LED, SW, SG, SA);

input CLK6;

input [3:0] SW;

output [7:0] LED, SG;

output [3:0] SA;

reg [3:0] r0, r1, pc; // register (r0/r1) & pc

wire [3:0] iaddr, op, imm; // iaddr, op, imm

wire [7:0] idata; // idata

wire [3:0] d3, d2, d1, d0;

reg st, z;

wire clk, rst;

imem i0(iaddr, idata); // instruction memory

sw_clk iclk(CLK6, ~SW[0], clk); // clock

seg7 iseg7(CLK6, d3, d2, d1, d0, SG, SA); // 7segment LED display

assign rst = ~SW[3]; // SW[3]:reset

assign op = idata[7:4], imm = idata[3:0];

assign iaddr = pc;

// LED display assignment

assign LED = {z, st, clk, 1'b0, op};

// 7segment display assignment

assign d3 = 4'd0, d2 = iaddr, d1 = r1, d0 = r0;

always @(posedge clk or posedge rst) begin

if (rst == 1'b1) begin

// reset

pc <= 4'h0; st <= 1'b0; z <= 1'b0; r0 <= 4'h0; r1 <= 4'h0;

end

else begin

// CPU state machine

// ......

end

end

endmodule

偙偙偱僋儘僢僋惗惉偺sw_clk偲7僙僌儊儞僩LED惂屼偺7seg偼丄

peripheral.v偺拞偱婰弎偝傟偰偄偰丄偙偙偱偼偦傟傪

僀儞僗僞儞僗屇傃弌偟偟偰棙梡偟偰偄傑偡丅

(嫽枴偑偁傞恖偼peripheral.v偺拞恎傪偺偧偄偰傒偰偔偩偝偄)

seg7偼丄4價僢僩偺d0乣d3偵梌偊傜傟傞抣傪奺寘偺7僙僌儊儞僩LED偵

帺摦揑偵昞帵偟傑偡丅

(d0偑嵟壓埵(塃抂)丄d3偑嵟忋埵(嵍抂)丅抣偼0乣9/A乣F偺16恑昞婰)

墘廗2-1

偙偺sample.v偱丄7僙僌儊儞僩LED偺奺寘偲8屄偺LED偵昞帵偝傟傞忣曬偑

壗偵側傞偐傪棟夝偟傑偟傚偆丅

傑偨奺僀儞僗僞儞僗娫偺愙懕傗巊傢傟偰偄傞怣崋傪棟夝偟傑偟傚偆丅

(椺偊偽柦椷op傗懄抣imm偺嶌傝曽側偳)

柦椷儊儌儕

柦椷儊儌儕偼丄梌偊傜傟偨傾僪儗僗iaddr偵懳偟偰丄

偦偺斣抧偺儊儌儕偺撪梕傪idata偵弌椡偡傞夞楬丄偲峫偊傞偙偲偑偱偒傑偡丅

偙傟偼丄尒曽傪曄偊傞偲丄擖椡iaddr偵墳偠偰弌椡idata偑寛傑傞夞楬丄

偲偄偆偙偲偱偡偺偱丄慻傒崌傢偣榑棟夞楬偲峫偊傞偙偲偑偱偒傑偡丅

偡側傢偪丄慜夞偺2-4僨僐乕僟偲摨條偵婰弎偡傞偙偲偑偱偒傞偱偟傚偆丅

偡側傢偪奣棯偼埲壓偺捠傝偵側傝傑偡丅

// Instruction Memory

module imem(addr, data);

input [3:0] addr;

output [7:0] data;

reg [7:0] data;

always @(addr) begin

case (addr)

....

endcase

end

endmodule

墘廗2-2

僾儘僕僃僋僩偵怴偟偄僼傽僀儖imem.v傪File仺New仺(Verilog僼傽僀儖)偱捛壛偟丄

埲壓偺傛偆側僾儘僌儔儉傪奿擺偡傞柦椷儊儌儕imem偺VerilogHDL婰弎傪

捛壛偟偰傒傑偟傚偆丅

傑偨偦偺摦嶌傪僔儈儏儗乕僔儑儞偱妋擣偟偰偍偒傑偟傚偆丅

| 斣抧(iaddr) | 柦椷(idata) | 柦椷偺僯乕儌僯僢僋昞婰 |

| 0 | 0000 0001 | mov 1, r0 |

| 1 | 0001 0010 | mov 2, r1 |

| 2 | 0110 0010 | jmp 2 |

僔儈儏儗乕僔儑儞偺峴偄曽偼丄婎杮揑偵偼慜夞偲摨條偱偡偑丄崱夞梌偊傞怣崋偼iaddr偱4價僢僩偱偡偺偱丄怣崋傪壛偊傞(Insert)偲偒偵丄"BusWidth"(僶僗暆=壗價僢僩偐偲偄偆偙偲)傪乽4乿偲偟偰偍偗偽丄4價僢僩偺抣(10恑悢偱0乣15)偲偟偰怣崋傪梌偊傞偙偲偑偱偒傑偡丅

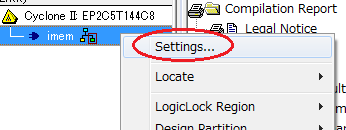

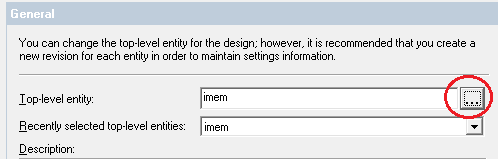

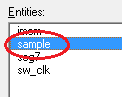

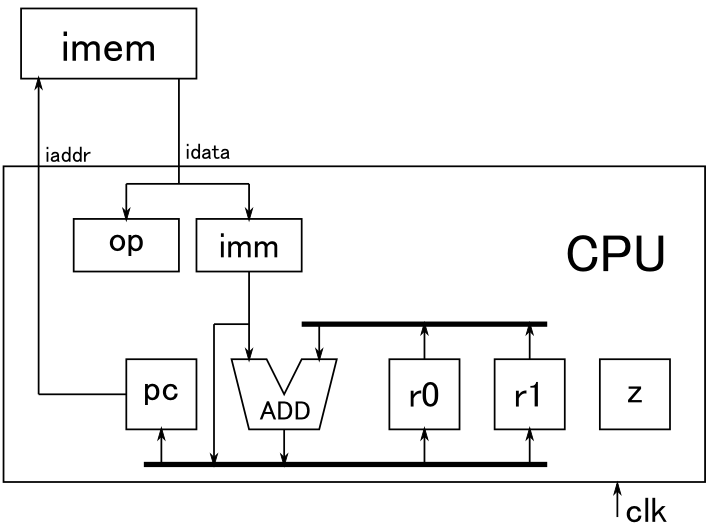

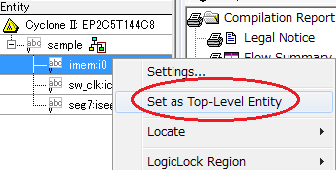

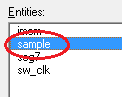

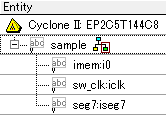

仸偙偺応崌偺傛偆偵丄嵟忋埵奒憌偺夞楬(偙偺応崌偼sample)偺拞偵偁傞夞楬偵懳偟偰僔儈儏儗乕僔儑儞傪峴偆偵偼丄堦帪揑偵僔儈儏儗乕僔儑儞傪峴偄偨偄夞楬傪埲壓偺庤弴偱嵟忋埵奒憌(Top Level)偵偡傞昁梫偑偁傝傑偡丅(僔儈儏儗乕僔儑儞偑廔傢偭偨傜丄杮棃偺嵟忋埵奒憌偺sample傪嵟忋埵奒憌偵栠偡)

傑偨暋悢偺夞楬偵懳偟偰丄暿乆偺擖椡怣崋攇宍傪巊偄偨偄応崌偼丄埲壓偺傛偆偵屄暿偵巜掕偡傞偙偲偑偱偒傑偡丅

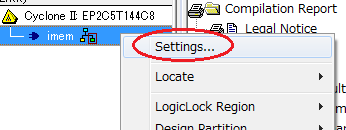

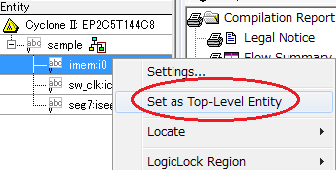

仾嵟忋埵奒憌偵偟偨偄夞楬(偙偺応崌偼imem)傪慖傫偱塃僋儕僢僋仺"Set as Top-Level Entity"(偙傟偱偙偺imem偑嵟忋埵奒憌偵側傞)

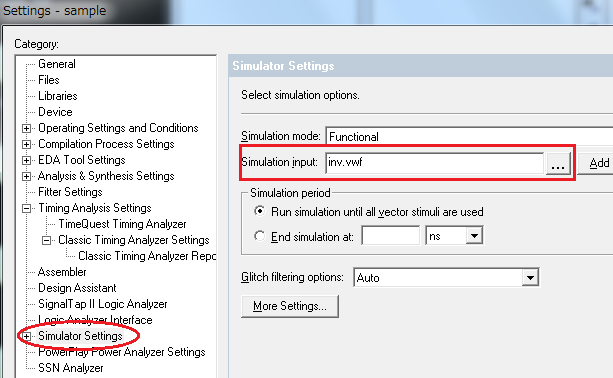

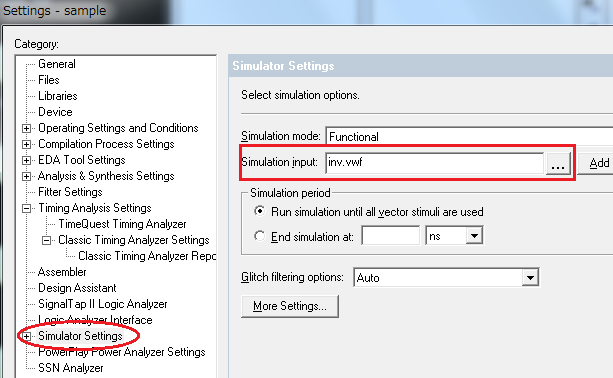

偙偺夞楬偵懳偟偰丄嵟弶偵嶌偭偨擖椡怣崋攇宍(*.vwf)偲偼暿偺擖椡怣崋攇宍傪梌偊偰僔儈儏儗乕僔儑儞傪峴偄偨偄応崌偼丄偦偺夞楬傪塃僋儕僢僋仺"Settings"偐傜丄僇僥僑儕乕"Simulator Settings"偱"Simulation input"偺偲偙傠偱巊偄偨偄擖椡怣崋攇宍僼傽僀儖(*.vwf)傪巜掕偡傟偽傛偄丅

仸側偍擖椡怣崋攇宍僼傽僀儖偱怣崋傪梌偊傞擖椡怣崋傪擖椡偡傞偲偒丄怣崋偺庬椶(Type)偑"Input"埲奜(偨偲偊偽Buried)偲側偭偰偟傑偆偙偲偑偁傞傛偆偱偡丅偦偺応崌偼丄怣崋柤傪塃僋儕僢僋仺Property偐傜丄"Type"傪"Input"偵巜掕偟偰偍偄偰偔偩偝偄丅

"Input"

"Input"

"Buried"

"Buried"

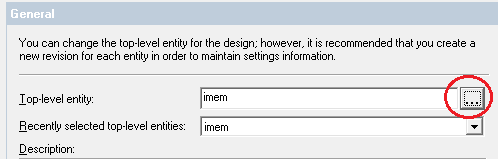

埲壓偼丄栠偡偲偒偺庤弴丅

仾栠偡偲偒偼丄傑偢尰嵼偺嵟忋埵奒憌偺imem傪慖傫偱塃僋儕僢僋仺"Settings"

仾Top-level entity偺偲偙傠偵尰嵼偺imem偑昞帵偝傟偰偄傞偺偱丄偦偺塃偺"..."儃僞儞傪墴偡

仾嵟忋埵奒憌偵曄峏偡傞夞楬傪慖傇夋柺偵側傞偺偱丄杮棃偺嵟忋埵奒憌偱偁傞samplpe傪慖傫偱OK傪墴偡

仾嵟弶偺奒憌峔憿偱偁傞丄嵟忋埵奒憌=sample丄偦偺拞偵imem摍丄偺峔憿偲側傞

CPU偺HDL婰弎

偝偒傎偳偺sample_cpu撪偺sample.v偺丄

嵟屻偺曽偺CPU state machine晹暘偵丄柦椷傪幚峴偡傞夞楬傪婰弎偡傟偽

CPU偲偟偰姰惉偟傑偡丅

奺柦椷偺幚峴偼丄st=0忬懺偲st=1忬懺傪岎屳偵孞傝曉偡偙偲偵側傝丄

奺忬懺偱偼師偺傛偆側摦嶌傪峴偆偙偲偵側傝傑偡丅

- 僗僥僢僾0(st=0)

- 撉傒弌偟偨柦椷idata偺op偵墳偠偰丄

揔愗側儗僕僗僞偵抣傪柦椷幚峴撪梕偺戙擖偡傞丅

(椺偊偽op="0000"側傜偽懄抣imm傪r0偵戙擖)

- Z僼儔僌偺抣傪峏怴偡傞丅

(椺偊偽op="0000"(mov imm, r0)偱imm=0側傜偽Z=1偲偡傞)

- 僗僥僢僾1(st=1)

- pc傪峏怴偡傞丅

(jmp柦椷側傜偽imm傪pc偵戙擖丅

jz柦椷側傜偽Z=1偺偲偒偼imm傪pc偵戙擖丅

偦傟埲奜側傜偽pc傪+1偡傞)

偮傑傝丄mov傗add偼乽st=0偱偺儗僕僗僞傊偺戙擖乿偲偟偰丄

暘婒柦椷偼乽st=1偱偺pc傊偺戙擖乿偲偟偰婰弎偡傞偙偲偑偱偒傞偙偲偵側傝傑偡丅

墘廗2-3

CPU偺婰弎傪姰惉偝偣丄imem偲偁傢偣偰僀儞僾儕儊儞僥乕僔儑儞偟丄

僔儈儏儗乕僔儑儞偱偺専徹傗幚婡偱偺摦嶌傪妋擣偟偰傒傑偟傚偆丅

仸(曗懌)CPU慡懱偺僔儈儏儗乕僔儑儞傪峴偆偲偒偵偼丄僋儘僢僋惗惉梡偺夞楬sw_clk偵僋儘僢僋怣崋(偙偺幚尡偱巊偭偰偄傞FPGA儃乕僪偱偼6MHz)傪梌偊傞昁梫偑偁傝傑偡丅

(杮棃偼7僙僌儊儞僩LED昞帵夞楬seg7偵傕昁梫)偙傟偼丄sw_clk偑乽僗僀僢僠傪墴偟偰偐傜堦掕帪娫偩偗弌椡clk=1偲偡傞乿偲偄偆摦嶌偺偨傔偵僋儘僢僋怣崋CLK6傪巊偭偰偄傞偨傔偱偡丅(徻偟偔偼peripheral.v撪偺sw_clk偺婰弎傪嶲徠)

偦偺偨傔僔儈儏儗乕僔儑儞偱傕偙偺CLK6傪擖椡偲偟偰梌偊傞昁梫偑偁傝傑偡偑丄sw_clk偺摦嶌傪尒傞偲傢偐傞傛偆偵丄CLK6偺90枩僒僀僋儖暘偩偗clk=1偲偡傞丄偲偄偆摦嶌偺偨傔丄偙傟傪僔儈儏儗乕僔儑儞偱専徹偡傞偺偼岠棪偑傛偔偁傝傑偣傫偟尰幚揑偱偼偁傝傑偣傫丅

偦偙偱丄僔儈儏儗乕僔儑儞梡偵peripheral.v撪偵彂偄偰偁傞sw_clk偺婰弎傪僐儊儞僩傾僂僩偟偨忋偱師偺傛偆偵彂偒姺偊丄CLK6傪巊傢偢偵僗僀僢僠偐傜僋儘僢僋怣崋clk傪嶌傞傛偆偵偟偨偆偊偱僔儈儏儗乕僔儑儞傪峴偆偲傛偄偱偟傚偆丅

module sw_clk(CLK6, a, q);

input CLK6, a;

output q;

assign q = a;

endmodule

傕偪傠傫僔儈儏儗乕僔儑儞偑廔傢偭偰FPGA儃乕僪偵彂偒崬傓偲偒偵偼丄sw_clk傪栠偡偺傪偍朰傟側偔丅

仸(曗懌)CPU摦嶌偺僔儈儏儗乕僔儑儞偱偼丄CPU傪婰弎偟偰偄傞sample偺弌椡偑LED偲SG偲SA乮偄偢傟傕LED傗7僙僌儊儞僩LED偺怣崋)偺偨傔丄妋擣偑偟偵偔偄偱偡丅(摿偵SA偲SG偼seg7偵傛偭偰僟僀僫儈僢僋嬱摦偝傟傞怣崋偺偨傔丄偳偺傛偆側弌椡偑弌偰偄傞偺偐丄偑傢偐傝偵偔偄乯

偦偙偱丄堦帪揑偵丄僔儈儏儗乕僔儑儞偱娤應偟偨偄怣崋傪sample偺弌椡偲偟偰掕媊偟偰僔儈儏儗乕僔儑儞傪峴偆丄偲偄偆曽朄偑曋棙偱偡丅

偨偲偊偽怣崋d0傪娤應偡傞側傜偽丄埲壓偺傛偆偵婰弎偟傑偡丅

//module sample(CLK6, LED, SW, SG, SA); // comment out

module sample(CLK6, LED, SW, SG, SA, d0); // added

output [3:0] d0; // added

傕偪傠傫僔儈儏儗乕僔儑儞偑廔傢偭偰FPGA儃乕僪偵彂偒崬傓偲偒偵偼丄sw_clk傪栠偡偺傪偍朰傟側偔丅

偄傠偄傠側僾儘僌儔儉偺幚峴

偙偙偱愝寁偟偨CPU偼丄柦椷偑8庬椶偟偐偁傝傑偣傫偑丄

偙傟偱傕偄傠偄傠側僾儘僌儔儉傪幚峴偱偒傑偡丅

椺偊偽師偺傛偆側僾儘僌儔儉傪梌偊偰傒傑偡丅

| 斣抧(iaddr) | 柦椷(idata) | 柦椷偺僯乕儌僯僢僋昞婰 |

| 0 | 0000 0000 | mov 0, r0 |

| 1 | 0001 0011 | mov 3, r1 |

| 2 | 0010 0100 | add r0, 4, r0 |

| 3 | 0101 1111 | add r1, 15, r1 |

| 4 | 0111 0110 | jz 6 |

| 5 | 0110 0010 | jmp 2 |

| 6 | 0110 0110 | jmp 6 |

墘廗2-4

忋婰偺僾儘僌儔儉偺摦嶌傪棟夝偟丄imem偺撪梕傪偙傟偵偁傢偣偰曄峏偟偰

僾儘僌儔儉傪幚峴偝偣丄寢壥傪妋擣偟偰傒傑偟傚偆丅

仸僸儞僩: 3斣抧偺"add r1, 15, r1"偼丄乽r1+15仺r1乿偩偑丄

r1偼4價僢僩偱寘偁傆傟偼柍帇偡傞丅

椺偊偽r1=3偱偙偺柦椷傪幚峴偡傞偲丄r1+15=18(2恑悢偱1 0010)偩偑

寘偁傆傟偼柍帇偡傞偺偱r1=2偲側傞丅偡側傢偪-1(尭嶼)傪峴偭偰偄傞偙偲偵側傞丅

墘廗2-5

偙傟傜偺柦椷傪巊偭偰撈帺僾儘僌儔儉傪嶌惉偟丄偦偺摦嶌傪妋擣偟偰傒傑偟傚偆丅

栠傞

"Input"

"Input"

"Buried"

"Buried"