偙偺傛偆側丄搑拞偺僲乕僪(怣崋)偼丄wire暥偱愰尵傪偡傞偙偲偑偱偒傑偡丅 偨偲偊偽偙偺夞楬拞偺丄愒栴報偺怣崋慄偵 hoge 偲偄偆柤慜傪偮偗偰丄 偙偺夞楬慡懱傪婰弎偡傞偲丄師偺傛偆偵側傝傑偡丄

崱夞偼丄偙傟傜偺栤戣傪夝寛偡傞傕偺偲偟偰嬤擭媫懍偵晛媦偟偰偒偨丄 尵岅(Hardware Description Language; HDL)偵傛傞榑棟夞楬愝寁傪 峴偭偰傒傑偡丅 偙偺幚尡偱偼丄摿偵VerilogHDL偲偄偆HDL尵岅傪梡偄傞偙偲偵偟傑偡丅

// sample module module sample(SW, LED); input [1:0] SW; output [1:0] LED; assign LED[0] = SW[0]; assign LED[1] = SW[1]; endmodule偙偺椺偱偼丄"sample"偲偄偆柤慜偺夞楬(module)傪掕媊偟偰偄傑偡丅 嵟弶偺module偺屻偵夞楬偺柤徧傪彂偒丄偦偺偁偲偺妵屖撪偵丄 偦偺夞楬偺擖椡偲弌椡偺柤徧傪婰弎偟傑偡丅 偙偙偱偼丄FPGA儃乕僪忋偵偁傞丄慜夞傕梡偄偨LED[0]乣LED[1]偲 SW[0]乣SW[1]傪梡偄傞偙偲傪婰弎偟偰偄傑偡丅

懕偄偰丄夞楬偺婰弎偵擖傝傑偡偑丄傑偢偼擖椡偲弌椡偺柤徧偲丄 偦傟傜偑擖椡偲弌椡偺偄偢傟偐側偺偐丄傪婰弎偟偰偄傑偡丅 偙偺椺偱偼丄SW[0]乣SW[1]傪擖椡(input)丄LED[0]乣LED[1]傪弌椡(output)偲 婰弎偟偰偄傑偡丅

偦偺屻偑偄傛偄傛夞楬帺懱偺婰弎偵側傝傑偡丅 偙偺応崌偼丄assgin(妱傝摉偰)暥偲偄偆婰弎曽朄傪梡偄偰丄 弌椡偱偁傞LED[0]偵丄擖椡偱偁傞SW[0]傪妱傝摉偰丄偡側傢偪 愙懕偟偰偄傑偡丅 摨條偵LED[1]偵偼SW[1]傪愙懕偟偰偄傑偡丅

嵟屻偼丄endmodule暥偱丄夞楬偺婰弎偑廔傢傞偙偲傪帵偟傑偡丅 偪側傒偵1峴栚偺傛偆偵丄//偐傜巒傑傞峴偼僐儊儞僩偵側傝傑偡丅

| 斲掕(NOT) | ~ |

| 榑棟愊(AND) | & |

| 榑棟榓(OR) | | |

| 攔懠揑榑棟榓(XOR) | ^ |

assign LED[0] = SW[0] | SW[1];偙偺傛偆偵丄VerilogHDL偱偼丄傎偲傫偳榑棟幃傪偦偺傑傑彂偔偩偗偱 夞楬偲偟偰婰弎偑姰椆偡傞偙偲偵側傝傑偡丅 偝傜偵丄榑棟幃偺娙棯壔偼丄帺摦揑偵峴偭偰偔傟傑偡偺偱丄 僇儖僲乕恾側偳偲偵傜傔偭偙傪偡傞昁梫偼丄傎偲傫偳偁傝傑偣傫丅

側偍夞楬偺拞偵偼丄input傗output偱掕媊偝傟傞擖弌椡埲奜偵傕丄

偨偲偊偽師偺傛偆偵丄夞楬偺搑拞偺乽僲乕僪(怣崋)乿偑

偁傞偙偲傕偁傝傑偡丅

偙偺傛偆側丄搑拞偺僲乕僪(怣崋)偼丄wire暥偱愰尵傪偡傞偙偲偑偱偒傑偡丅

偨偲偊偽偙偺夞楬拞偺丄愒栴報偺怣崋慄偵 hoge 偲偄偆柤慜傪偮偗偰丄

偙偺夞楬慡懱傪婰弎偡傞偲丄師偺傛偆偵側傝傑偡丄

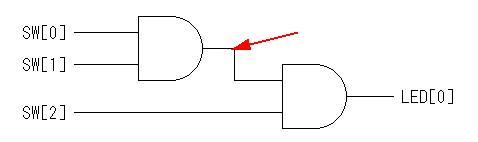

module sample(SW, LED); input [3:0] SW; output [3:0] LED; wire hoge; assign hoge = SW[0] & SW[1]; assign LED[0] = hoge & SW[2]; endmoduleassign暥偑2偮偁傝丄1偮栚偱嵍懁偺AND僎乕僩丄 2偮栚偱塃懁偺AND僎乕僩傪婰弎偟偰偄傑偡丅 側偍偙偺assign暥偼丄C尵岅側偳偺僾儘僌儔儉偵偍偗傞乽戙擖乿偺傛偆偵 尒偊傑偡偑丄幚嵺偵偼丄偙偺彂偄偰偁傞弴彉偱乽抣偺戙擖乿偑婲偙傞偺偱偼側偔丄 偁偔傑偱傕乽AND僎乕僩偲偄偆夞楬偑偁傞乿偙偲傪婰弎偟偰偄傞偺偱偡丅 偮傑傝丄1偮栚偺assign暥偱丄傑偢偼hoge偺抣偑妋掕偟丄 偦傟傪巊偭偰2偮栚偺assign暥偱LED[0]偺抣傪媮傔傞丄偲偄偆傢偗偱偼 偁傝傑偣傫偺偱丄偙偺2偮偺assign暥偺弴彉傪擖傟懼偊偰傕丄 傑偭偨偔摦嶌偼曄傢傝傑偣傫丅

椺偲偟偰丄2價僢僩偺擖椡(d[0], d[1])偵墳偠偰丄4杮偺弌椡(q[0]乣q[3]) 偺偆偪偺1偮偺傒偑1偲側傞傛偆側乽2 to 4僨僐乕僟乿傪傒偰傒傑偟傚偆丅 偙偺夞楬偺恀棟抣昞偼師偺傛偆偵側傝傑偡丅

| d[1] | d[0] | q[0] | q[1] | q[2] | q[3] | |

| 0 | 0 | 1 | 0 | 0 | 0 | |

| 0 | 1 | 0 | 1 | 0 | 0 | |

| 1 | 0 | 0 | 0 | 1 | 0 | |

| 1 | 1 | 0 | 0 | 0 | 1 |

module sample(SW, LED);

input [1:0] SW;

output [3:0] LED;

wire [1:0] d;

reg [3:0] q;

assign d = {SW[1], SW[0]};

assign LED = q;

always @(d) begin

case (d)

2'b00 : q <= 4'b0001;

2'b01 : q <= 4'b0010;

2'b10 : q <= 4'b0100;

2'b11 : q <= 4'b1000;

endcase

end

endmodule

堦婥偵暋嶨搙偑憹偟傑偟偨偑丄弴傪捛偭偰傒偰偄偒傑偟傚偆丅

嵟弶偺module暥丄input暥丄output暥偼丄愭傎偳偲摨偠偱偡丅

懕偔wire暥偱偼丄夞楬偺拞偱梡偄傞乽僲乕僪乿(怣崋)偲偟偰"d"傪 愰尵偟偰偄傑偡丅 偟偐傕"wire [1:0]"偲婰弎偡傞偙偲偱丄幚偼乽1斣乿偐傜乽0斣乿偺 2杮傪傑偲傔偰丄攝楍偺傛偆偵庢傝埖偆偙偲偑偱偒傑偡丅 偙偺椺偱偼丄幚嵺偵偼d[0]偲d[1]傪愰尵偟偰偄傞偙偲偵側傝傑偡丅

懕偔reg暥偱偼丄wire暥偲摨條偵丄夞楬偺拞偱梡偄傞僲乕僪偲偟偰丄 4價僢僩暆偺q傪愰尵偟偰偄傑偡偑丄wire暥偲堎側傝丄 偦偺抣偑丄屻偱弌偰偔傞always暥偺拞偱曄峏(掕媊)偡傞偙偲偑偱偒傞丄 偲偄偆惈幙傪帩偪傑偡丅 偙偺wire偲reg偺巊偄暘偗傪愢柧偡傞偺偼側偐側偐擄偟偄偺偱丄 幚椺傪偄傠偄傠尒傞偺偑桳岠偱偟傚偆丅 偲傝偁偊偢偼

懕偄偰丄wire暥偱愰尵偟偨2價僢僩暆偺僲乕僪d偵丄SW[1]偲SW[0]傪 愙懕偟偰偄傑偡丅 偙偺椺偱偼丄拞妵屖{}傪梡偄偰偄傑偡偑丄偙傟偵傛傝丄 2偮埲忋偺怣崋慄傪傑偲傔偰庢傝埖偆偙偲偑偱偒傑偡丅 傕偪傠傫椉曈偺暆偑摨偠応崌偼丄師偺傛偆偵婰弎偟偰傕偐傑偄傑偣傫丅 嬶懱揑偵偼丄偙偺婰弎偼丄幚嵺偵偼師偺傕偺偲摍壙偵側傝傑偡丅

assign d = SW;懕偔assign暥偱傕丄弌椡偱偁傞LED[0]乣LED[3]偵丄僲乕僪q[0]乣q[3]傪 愙懕偟偰偄傑偡丅

懕偄偰丄偙偺夞楬偺婰弎偺拞怱晹偱偁傞丄always暥偵側傝傑偡丅 偙傟偼丄塸暥偺傛偆偵婰弎傪撉傓偲堄枴偑傢偐傝傗偡偄偱偟傚偆丅 "always @(=at) d"丄偮傑傝丄乽d偱偄偮傕乿偲偄偆堄枴偵側傝傑偡偑丄 偙傟偼丄乽d偑曄壔偡傞偲偒偼偄偮傕乿偲撉傒懼偊傑偡丅

偦偺屻偺begin乣end偱偼偝傑傟偨晹暘偱丄 偦偺d偑曄壔偡傞偲偒偵丄幚嵺偵峴偆摦嶌傪婰弎偟偰偄傑偡丅 偙偙偱偼丄case暥傪梡偄偰丄d偺抣偵墳偠偰丄応崌暘偗傪偟偰偄傑偡丅 嬶懱揑偵偼丄d偑2'b00(乽2寘偺2恑悢(binary)偺00乿 偺堄枴)偺偲偒偵偼丄q偵4'b0001(乽4寘偺2恑悢偺0001乿)傪 戙擖偡傞丄偲掕媊偟偰偄傑偡丅 (4'b0001偼丄嵟壓埵偺傒偑1偱丄偙偺1偼q[3]偱偼側偔丄q[0]偵戙擖偝傟傞偙偲偵 拲堄偟傑偟傚偆丅偮傑傝嵟忋埵偑q[3]丄嵟壓埵偑q[0]偱偡丅媡偱偼偁傝傑偣傫丅) 摨條偵丄d偑2'b01丄2'b10丄2'b11偺応崌傕丄q偵戙擖偝傟傞傋偒 抣傪掕媊偟偰偄傑偡丅 嵟屻偵丄end暥偱begin暥傪暵偠丄偝傜偵endcase暥偱case暥傪暵偠偰偄傑偡丅

偙傟偵傛傝丄2寘偺2恑悢偱偁傞d偺抣偵墳偠偰丄 q[0]乣q[3]偺偄偢傟偐偺傒偑1偲側傞夞楬丄偡側傢偪 僨僐乕僟(2 to 4 decoder)偑偱偒傞偙偲偵側傝傑偡丅

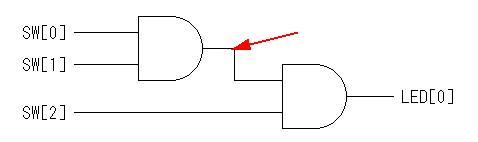

module sample(SW, LED); input [1:0] SW; output [1:0] LED; inv i0(SW[0], LED[0]); inv i1(SW[1], LED[1]); endmodule module inv(a, x); input a; output x; assign x = ~a; endmodule偙偺椺偱偼丄屻敿偱婰弎偟偰偄傞"inv"偲偄偆柤慜偺儌僕儏乕儖(幚懱偼 僀儞僶乕僞)傪丄慜敿偺儌僕儏乕儖sample撪偱梡偄偰偄傑偡丅 傑偢嵟弶偵丄i0偲偄偆柤徧偱儌僕儏乕儖inv偺婡擻傪帩偮夞楬傪嶌傝丄 偦偺擖椡(偙偺応崌偼戞1堷悢)偲弌椡(偙偺応崌偼戞2堷悢)偵丄 偦傟偧傟SW[0]偲LED[0]傪愙懕偟偰偄傑偡丅 摨條偵丄傕偆1偮偺僀儞僶乕僞i1傪嶌偭偰丄偦偺擖椡偵SW[1]傪丄弌椡偵LED[1]傪 愙懕偟偰偄傑偡丅

偙偺夞楬傪僐儞僷僀儖偡傞偲丄嵟忋埵儌僕儏乕儖(懠偐傜

屇傃弌偝傟偰偄側偄儌僕儏乕儖)偑丄慡懱夞楬偲偟偰埖傢傟傞偙偲偵側傝傑偡丅

寢壥偲偟偰丄師偺傛偆側夞楬偑嶌傜傟傞偙偲偵側傝傑偡丅

側偍偙偙偱偼丄夞楬傪乽屇傃弌偡乿偲偄偆昞尰傪巊偄傑偟偨偑丄

幚嵺偵偼丄C尵岅側偳偺娭悢傪屇傃弌偟偰抣偺戙擖傪幚峴偡傞丄

偲偄偆傢偗偱偼側偔丄偙偺夞楬恾偺傛偆偵丄

乽僀儞僶乕僞偑2偮嶌傜傟傞乿(乽僀儞僶乕僞偑2偮偁傞偙偲傪婰弎偟偰偄傞乿)

偙偲偵拲堄偟傑偟傚偆丅

偙偺傛偆側夞楬偺屇傃弌偟偱愙懕偝傟傞僲乕僪偼丄昁偢wire宆傪 梡偄傑偡丅 偨偲偊偽愭傎偳偺2偮偺AND僎乕僩偐傜側傞夞楬(搑拞僲乕僪偼hoge)偼 師偺傛偆偵彂偔偙偲傕偱偒傑偡丅

module sample(SW, LED); input [3:0] SW; output [3:0] LED; wire hoge; and_2 i0(SW[0], SW[1], hoge); and_2 i1(hoge, SW[2], LED[0]); endmodule module and_2(a, b, x); input a, b; output x; assign x = a & b; endmodule側偍偙偺傛偆側夞楬偺屇傃弌偟偱傕丄幚嵺偵偼乽AND僎乕僩偑2偮嶌傜傟傞乿 (乽AND僎乕僩偑2偮偁傞夞楬傪婰弎偟偰偄傞乿)傢偗偱偡偐傜丄 2偮偺AND僎乕僩傪屇傃弌偡婰弎偺弴彉傪媡偵偟偰傕丄 傑偭偨偔摨偠夞楬偑嶌傜傟傑偡丅 傑偨偙傟偼丄偁偔傑偱傕乽夞楬傪嶌傞乿婰弎偱偡偺偱丄 愭傎偳偺always暥偺拞偱丄師偺傛偆偵巊偆偙偲傕偱偒傑偣傫丅

always @(d) begin

case (d)

2'b00 : begin q <= 4'b0000; and_2 i0(d[0], d[1], hoge); end

...

偮傑傝丄偁偔傑偱傕乽夞楬(偙偺椺偱偼i0偲偄偆柤慜偺and_2)傪嶌傞乿

偙偲傪彂偔偺偼1夞偩偗偟偐偱偒偢丄偦傟偼always暥偺奜偱彂偔傋偒傕偺偱丄

always暥側偳偺拞偱丄乽偁傞忦審偺偲偒偩偗夞楬嶌傞乿偙偲偼偱偒傑偣傫丅

module sample(SW, LED);

input [3:0] SW;

output [3:0] LED;

reg [3:0] q;

assign LED = q;

always @(negedge SW[0] or negedge SW[1]) begin

if (SW[0] == 1'b0) begin

q <= 4'b0000;

end

else begin

q <= q + 1;

end

end

endmodule

偙偺椺偱偼丄always暥偺妵屖撪偵丄negedge偲偄偆彂偄偰偁傝傑偡丅

偙傟偼丄怣崋偺棫偪壓偑傝(negative edge)傪帵偡傕偺偱丄

"negedge SW0"偲偐偔偲丄乽怣崋SW0偺棫偪壓偑傝乿偲偄偆堄枴偵側傝傑偡丅

偙偺椺偱偼丄2偮偺忦審傪"or"偱暲傋偰偄傑偡偺偱丄

乽SW[0]偺棫偪壓偑傝丄偁傞偄偼SW[1]偺棫偪壓偑傝乿偺偲偒偵丄

always暥撪偺婰弎偺摦嶌偑峴傢傟傞偙偲偵側傝傑偡丅

偦偺摦嶌偼丄if暥偱2偮偺応崌偵暘偐傟偰偄偰丄 乽SW[0]偑0偺偲偒乿(偮傑傝SW[0]偺棫偪壓偑傝丄偺偲偒)偼丄 q偵4寘偺0傪戙擖偟偰偄傑偡丅 偙偺戙擖偼丄乽<=乿偲偄偆墘嶼巕傪梡偄偰偄傑偡偑丄 偙傟偼丄偲傝偁偊偢偼乽僼儕僢僾僼儘僢僾偑擖傞夞楬偺偲偒乿偵 巊偆偲棟夝偟偰偍偄偰偔偩偝偄丅 偮傑傝SW[0]偺棫偪壓偑傝丄偡側傢偪SW[0]傪墴偟偨偲偒偵丄 q偑0偵儕僙僢僩偝傟傑偡丅

偦傟埲奜(else)丄偡側傢偪丄傕偆1偮偺忦審偱偁傞 乽SW[1]偑0偺偲偒乿(偮傑傝SW[1]偺棫偪壓偑傝丄偺偲偒)偼丄 q偵1傪壛偊偨傕偺傪丄師偺q偵戙擖偟偰偄傑偡丅 偡側傢偪SW[1]偺棫偪壓偑傝丄偡側傢偪SW[1]傪墴偡偨傃偵丄 q偺抣偼1偢偮傆偊偰偄偔丄偮傑傝僇僂儞僞偲偟偰摦嶌傪偡傞偙偲偵側傝傑偡丅

傑偨梋桾偑偁傟偽丄慜夞偲摨條偵丄僠儍僞儕儞僌杊巭夞楬傪捛壛偟偰傒傑偟傚偆丅 偙傟偼丄僠儍僞儕儞僌杊巭夞楬傪暿偺module偲偟偰婰弎偟丄 嵟忋埵儌僕儏乕儖(sample)偐傜屇傃弌偡丄偲偄偆宍幃傪偲傞偲 尒傗偡偄婰弎偲側傞偱偟傚偆丅

module sample(SW, LED);

input [3:0] SW;

output [3:0] LED;

wire co;

counter10 i0(SW[0], LED, co);

endmodule

module counter10(ck, q, co);

input ck;

output [3:0] q; // counter output

output co; // carry out

reg [3:0] q;

reg co;

always @(posedge ck) begin

if (q == 9) begin

q <= 0;

co <= 1;

end

else begin

q <= q + 1;

co <= 0;

end

end

endmodule

屻敿偱counter10偲偄偆柤徧偺夞楬傪婰弎偟丄偦傟傪慜敿偺慡懱夞楬偱偁傞

sample偱屇傃弌偟偰巊偭偰偄傑偡丅

偙偙偱co偲偄偆丄LED側偳偵偼愙懕偝傟偰偄側偄怣崋慄偑偁傝傑偡偑丄

偙傟偼偁偲偱巊偄傑偡偺偱丄偲傝偁偊偢偄傑偼柍帇偟偰偍偒傑偟傚偆丅

偙偺counter10偱偼丄僋儘僢僋怣崋ck偺棫偪忋偑傝偛偲偵

if暥傪巊偭偰丄q偺抣偵墳偠偰丄師偵q傪偳偺傛偆側抣偵偡傞偐傪

掕媊偟偰偄傑偡丅

嬶懱揑偵偼丄q(4價僢僩偺悢)偑9偱偁傟偽丄q偺抣傪0偵峏怴偟傑偡偑丄

偦傟埲奜偺偲偒偼丄師偵偼q偺抣傪q+1偵峏怴偡傞傛偆偵

婰弎偟偰偄傑偡丅

偙傟偵傛傝丄q偺抣偼丄ck偺棫偪忋偑傝偛偲偵丄

0仺1仺2仺丒丒丒仺8仺9仺0仺1仺丒丒丒

偲偄偆傛偆偵曄傢偭偰偄偔偙偲偵側傝傑偡丅

偙偺偨傔偵偼丄4價僢僩偺2恑悢傪7僙僌儊儞僩偺揰摂僷僞乕儞偵 曄姺偡傞丄7僙僌儊儞僩僨僐乕僟夞楬seg7_dec傪嶌傞昁梫偑偁傝傑偡丅 偙偺夞楬傪module偲偟偰婰弎偟偰偍偒丄慡懱夞楬偺儌僕儏乕儖偱偁傞 sample偐傜丄counter10偲偲傕偵屇傃弌偡宍偵偡傞偲丄 尒捠偟偺傛偄夞楬偺婰弎偵側傞偱偟傚偆丅

椺偊偽愭傎偳偺10恑僇僂儞僞偺寘忋偑傝弌椡co偼丄 僋儘僢僋ck偺10廃婜偛偲偵1僋儘僢僋暘偩偗1偲側傝傑偡丅 偮傑傝丄co偺廃攇悢偼丄ck偺廃攇悢偺1/10丄偲偄偆偙偲偵側傝傑偡丅 偙偺傛偆偵丄僋儘僢僋怣崋偺廃攇悢傪丄僇僂儞僞摍傪梡偄偰 掅偔偡傞偙偲傪暘廃偲屇傃傑偡丅

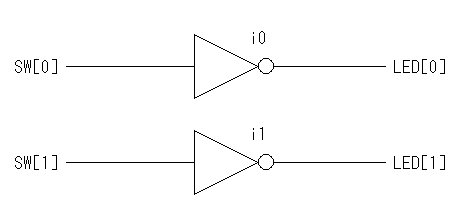

傑偢偼慡懱偺峔惉傪師偺傛偆偵惍棟偟偰偍偒傑偟傚偆丅

傑偢7僙僌儊儞僩LED偺奺寘傪僟僀僫儈僢僋嬱摦偱弴師揰摂偝偣傞偨傔偵丄

4恑僇僂儞僞counter4傪梡偄傞偙偲偵偟傑偡丅

偙偺弌椡qs[1:0]偼丄(1)昞帵偡傞傋偒7僙僌儊儞僩LED偺寘偺慖戰SA[3:0]丄 (2)偦偺7僙僌儊儞僩LED偵昞帵偡傞傋偒抣偲偟偰丄奩摉偡傞寘偺僇僂儞僞偺 弌椡傪慖戰偡傞select4丄偺2偮偵巊傢傟傑偡丅

7僙僌儊儞僩僨僐乕僟decode_7seg偼丄select4偵傛偭偰 慖偽傟偨僇僂儞僞偺抣(q0乣q3偺偄偢傟偐)偵墳偠偰丄 7僙僌儊儞僩LED偺揰摂僷僞乕儞傪嶌傝丄悢帤傪昞帵偟傑偡丅

慡懱偺僇僂儞僞偼4寘偺10恑僇僂儞僞偱偡偐傜丄 10恑僇僂儞僞counter10傪4屄丄屇傃弌偟偰愙懕偟傑偡丅 側偍丄奺寘偺愙懕曽朄偵偼丄 僇僂儞僞梡僋儘僢僋偑偡傋偰偺寘偺僇僂儞僞偵擖傞乽摨婜幃乿(偙偺恾)偲丄 奺寘偺僇僂儞僞偺僋儘僢僋傪丄慜偺寘偺寘忋偘怣崋co偐傜梌偊傞 乽旕摨婜幃乿偑偁傝傑偡丅 崱夞偼丄峔惉偑僔儞僾儖側乽旕摨婜幃乿偱廫暘偱偡偑丄 慜偺寘偺co偐傜丄師偺寘偺僋儘僢僋傪偳偺傛偆偵嶌惉偡傟偽傛偄偐丄 廫暘峫偊傑偟傚偆丅

側偍僟僀僫儈僢僋嬱摦梡僋儘僢僋偼CLK6傑偨偼CLK30傪 揔摉偵暘廃偟偰嶌惉偡傞偙偲偲偟丄 偦偺廃攇悢偼1kHz掱搙偑傛偄偱偟傚偆丅 (偁傑傝廃攇悢偑掅偄偲僠儔僣僉偑栚棫偪傑偡) 傑偨僇僂儞僞梡僋儘僢僋偼丄摨偠偔CLK6傑偨偼CLK30傪揔摉偵暘廃偟偰嶌惉偡傞偐丄 偁傞偄偼僗僀僢僠傪梡偄傞偲傛偄偱偟傚偆丅

偳偙偐傜庤傪偮偗偨傜傛偄偐尒摉偑偮偐側偄応崌偼丄傑偢偼揔摉側SG傪掕悢偱梌偊丄 SA傪弴師愗傝懼偊傞丄偲偄偆夞楬傪嶌傞偲偙傠偐傜偼偠傔傞偲傛偄偱偟傚偆丅 (偙偺愗傝懼偊傕丄嵟弶偼僗僀僢僠SW[0]偱愗傝懼偊傞丄側偳偱傕傛偄) 偦偺屻丄偦偺SA偵偁傢偣偰梌偊傞傋偒SG傪7僙僌儊儞僩僨僐乕僟偐傜嶌傞傛偆偵偟偰丄 嵟屻偵4寘廫恑僇僂儞僞傪偮側偖丄偲偄偆弴偱恑傔傞偲傛偄偱偟傚偆丅